AMQL64DAM22GG(NEW), AMQL64DAM22GG ATHLON 64 X2 QL-64 2.1GHZ 512KB S1G2 OBALB QBANB

Артикул: AMQL64DAM22GG(NEW)

Внимание! Серверные комплектующие являются запасными частями, и могут поставляться в ОЕМ упаковке (блистер, пластик, антистатический пакет). За подробной информацией о комплектации интересующего вас товара обращайтесь к менеджерам. Тел. +7(351)7000370

47 355 ₽

Процессор AMD AMQL64DAM22GG Athlon 64 X2 QL-64 2.1GHz 512KB S1g2 OBALB QBANB-AMQL64DAM22GG(NEW) теперь в вашей корзине покупок

К сравнению В избранное

Категории: Процессоры

Теги:

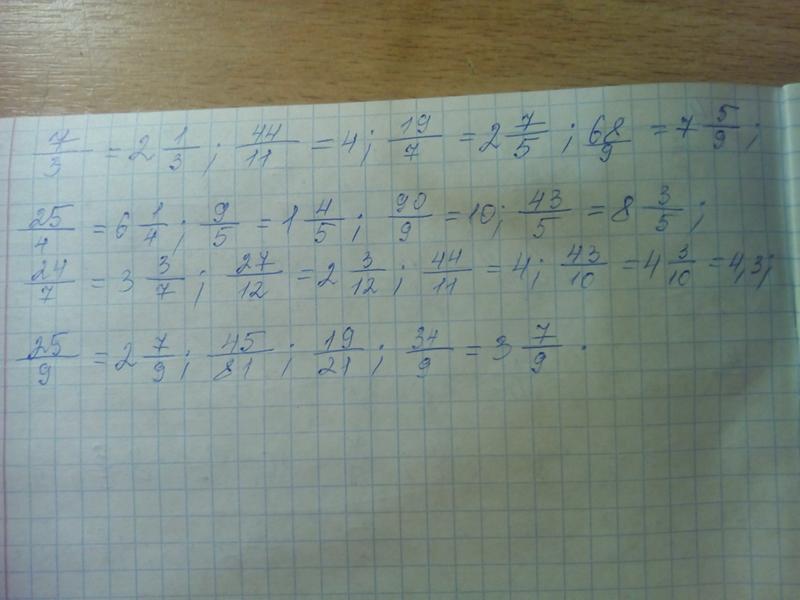

- Характеристики

- Обзор

- Доставка

Характеристики

| Склад | Срок поставки 2-3 недели |

| Кондиция | Товар новый |

| Подробно |

Процессоры — AMD Athlon 64 X2 QL-64 2. 1GHz 512KB S1g2 OBALB QBANB 1GHz 512KB S1g2 OBALB QBANBкупить новое оборудование, на гарантии, под заказ, под проект, с большой скидкой, по низким ценам, с доставкой по России, с доставкой по Казахстану, по выгодной це |

| Производитель | AMD |

Обзор

Процессоры — AMQL64DAM22GG Athlon 64 X2 QL-64 2.1GHz 512KB S1g2 OBALB QBANB

купить новое оборудование, на гарантии, под заказ, под проект, с большой скидкой, по низким ценам, с доставкой по России, с доставкой по Казахстану, по выгодной цене, по оптовым ценам, в рассрочку, в магазине СетиЛенд, Cisco, HP, Juniper, Dell, Intel, в Москве, доставка в Крым, доставка в Киргизию

Доставка

Самовывоз, доставка курьером, доставка до нужной транспортной компании.

— AMD — WikiChip Он был заменен Socket S1g3.

Основными улучшениями Socket S1g2 по сравнению с S1g1 являются поддержка HyperTransport поколения 3.0 и отдельные плоскости питания для каждого ядра и северного моста, функция энергосбережения. Процессоры S1g2 поддерживают двухплоскостные платформы, подающие одинаковое напряжение на оба ядра, но не поддерживают одноплоскостное питание северного моста.

Сокет S1g2 использовался в мобильной платформе AMD Puma. Все процессоры для Socket S1g2 входят в семейство процессоров AMD 11h.

Все версии Socket S1 имеют одинаковые размеры, однако процессоры для Socket S1g2 электрически несовместимы с Socket S1g1. Сокеты S1g2 и S1g3 имеют одинаковую распиновку, взаимозаменяемы ли процессоры для этих сокетов — непонятно. Процессоры Socket S1g2 не будут работать в системах Socket S1g4, в которых используется память DDR3, но процессоры S1g4, поддерживающие память DDR2 и DDR3, могут быть совместимы с Socket S1g2, если BIOS распознает ЦП.

Содержимое

- 1 Особенности

- 2 набора микросхем

- 3 процессора, использующие сокет S1g2

- 4 Схема упаковки

- 5 Контур гнезда

- 6-контактная карта

- 6.1 Описание контакта

- 7 Каталожные номера

- 8 См. также

Характеристики[править]

- 638-контактный безкрышный корпус с микроконтактной решеткой, шаг 1,27 мм, 26 × 26 контактов, 35 × 35 мм, органическая подложка, крепление матрицы C4 (флип-чип)

- 16-битный интерфейс HyperTransport 3.0 до 1800 МГц, 3600 МТ/с, 7,2 ГБ/с в каждом направлении

- 2 × 64-битный интерфейс DDR2 SDRAM до 400 МГц, PC2-6400 (DDR2-800) , 12,8 ГБ/с

- До 2 небуферизованных модулей SO-DIMM, без поддержки ECC

- JEDEC SSTL_1.8

- Управление питанием

- AMD PowerNow! технология

- До 8 P-состояний; ACPI C1, C1E, C2, C3, S1, S3, S5

- Самолеты с тройной силовой установкой

- Управление питанием канала HT

- Терморегуляторы

- Тепловая защита

- Аппаратный терморегулятор

- Тепловая защита DRAM

- Термодиод

Чипсеты[править]

- AMD M780G, M780V

- Драм 880М

- AMD SB700, SB710, SB820 южный мост

Процессоры, использующие Socket S1g20020

Схема упаковки[править]

Данные отсутствуют. Размеры должны быть такими же, как у корпуса OPGA-638, показанного на странице Socket S1g1.

Размеры должны быть такими же, как у корпуса OPGA-638, показанного на странице Socket S1g1.

Socket Outline #31839. Изображена технология Foxconn Interconnect Technology, часть № PZ6382A-284S-01F. Все размеры в миллиметрах.

Карта контактов[править]

Отличия от других версий Socket S1 см. в Socket S1g4.

Описание контакта[править]

| Сигнал | Описание |

|---|---|

| ALERT_L | Программируемый вывод, который может указывать на различные события, включая прерывание SB-TSI |

| CLKIN_H/L | Дифференциальная опорная частота ФАПЧ 200 МГц |

| DBREQ_L, DBRDY | Запрос отладки/готовность |

| HT_REF0, HT_REF1 | Компенсационный резистор HyperTransport для VSS, VLDT |

| КЛЮЧ1, КЛЮЧ2 | |

| L0_CADIN/OUT_H/L[15:0] | HT Link 0 Дифференциальная команда/адрес/ввод/вывод данных |

| L0_CLKIN/OUT_H/L[1:0] | HT Link 0 Дифференциальный тактовый вход/выход |

| L0_CTLIN_H/L[1:0] | HT Link 0 Дифференциальный вход/выход управления |

| LDTREQ_L | Канал HT активен или запрошен входом/выходом устройства |

| LDTSTOP_L | HT Вход управления остановкой для управления питанием и изменения ширины канала и частоты |

| MA0/MA1/MB0_CS_L[1:0], MB1_CS_L[0] | Выбор чипа DRAM |

| MA0/MA1/MB0_ODT[1:0], MB1_ODT[0] | Штырь включения DRAM для терминации на кристалле |

| MA/MB_ADD[15:0] | Адрес столбца/строки DRAM |

| МА/МБ_БАНК[2:0] | Адрес банка DRAM |

| МА/МБ_КАС_Л | Строб адреса столбца DRAM |

| MA/MB_CKE[1:0] | Включение часов DRAM |

| MA/MB_CLK_H/L[7/5/4/1] | Дифференциальный тактовый сигнал DRAM |

| MA/MB_DATA[63:0] | Шина данных DRAM |

| MA/MB_DM[7:0] | Маска данных DRAM |

| MA/MB_DQS_H/L[7:0] | Строб дифференциальных данных DRAM |

| МА/МБ_РАС_Л | Строб адреса строки DRAM |

| МА/МБ_WE_L | Разрешение записи DRAM |

| MEMHOT_L | Вход тепловой защиты DRAM |

| М_ВРЕФ | Опорное напряжение интерфейса DRAM |

| М_ЗП, М_ЗН | Компенсационный резистор для VSS, VDDIO |

| PROCHOT_L | Процессор в HTC-активном состоянии ввода/вывода |

| Напряжения и CLKIN достигли заданной работы | |

| СБРОС_L | Сброс процессора |

| РСВД | Зарезервировано |

| SIC, SID | Интерфейс датчика температуры боковой полосы (SB-TSI), часы, данные |

| СВК, СВД | Идентификатор последовательного напряжения, часы интерфейса, данные |

| ТСК, ТДИ, ТДО, ТМС, ТРСТ_Л | JTAG-интерфейс |

| ТЕСТ* | Тестовый сигнал |

| ТЕРМДА, ТЕРМДК | Термодиод Анод, Катод |

| ТЕРМТРИП_Л | Выход отключения термодатчика |

| VDD0 | Блок питания ядра 0 |

| VDD0_FB_H/L | Дифференциальная обратная связь к регулятору VDD0 |

| VDD1 | Блок питания ядра 1 |

| VDD1_FB_H/L | Дифференциальная обратная связь к регулятору VDD1 |

| ВДДА | Фильтрованное напряжение питания PLL |

| VDDIO | Блок питания кольца ввода/вывода DRAM |

| VDDIO_FB_H/L | Дифференциальная обратная связь к регулятору VDDIO |

| ВДНБ | Блок питания северного моста |

| ВДДНБ_ФБ_Х/Л | Дифференциальная обратная связь к регулятору VDDNB |

| VLDT_A/B | Блок питания кольца ввода/вывода HyperTransport |

| ВСС | Земля |

| ВТТ | Напряжение окончания DRAM |

| VTT_SENSE | Штифт монитора VTT |

Ссылки № 31839, версия 3.

01, 10 апреля 2007 г.

01, 10 апреля 2007 г.

См. также

Facts about «Socket S1g2 — AMD»

RDF feed

| designer | AMD + |

| first launched | June 4, 2008 + |

| instance of | package + |

| Сегмент рынка | Мобил + |

| Имя | Socket S1G2 + |

| TDP | |

| TDP | |

Socket S1g2 — AMD — WikiChip

Socket S1g2 был вторым сокетом для мобильных микропроцессоров AMD в упаковке OPGA-638 со встроенным контроллером памяти DDR2 и преемником Socket S1g1. Он был заменен Socket S1g3.

Основными улучшениями Socket S1g2 по сравнению с S1g1 являются поддержка HyperTransport поколения 3.0 и отдельные плоскости питания для каждого ядра и северного моста, функция энергосбережения. Процессоры S1g2 поддерживают двухплоскостные платформы, подающие одинаковое напряжение на оба ядра, но не поддерживают одноплоскостное питание северного моста.

Сокет S1g2 использовался в мобильной платформе AMD Puma. Все процессоры для Socket S1g2 входят в семейство процессоров AMD 11h.

Все версии Socket S1 имеют одинаковые размеры, однако процессоры для Socket S1g2 электрически несовместимы с Socket S1g1. Сокеты S1g2 и S1g3 имеют одинаковую распиновку, взаимозаменяемы ли процессоры для этих сокетов — непонятно. Процессоры Socket S1g2 не будут работать в системах Socket S1g4, в которых используется память DDR3, но процессоры S1g4, поддерживающие память DDR2 и DDR3, могут быть совместимы с Socket S1g2, если BIOS распознает ЦП.

Процессоры Socket S1g2 не будут работать в системах Socket S1g4, в которых используется память DDR3, но процессоры S1g4, поддерживающие память DDR2 и DDR3, могут быть совместимы с Socket S1g2, если BIOS распознает ЦП.

Содержимое

- 1 Особенности

- 2 набора микросхем

- 3 процессора, использующие сокет S1g2

- 4 Схема упаковки

- 5 Контур гнезда

- 6-контактная карта

- 6.1 Описание контакта

- 7 Каталожные номера

- 8 См. также

Характеристики[править]

- 638-контактный безкрышный корпус с микроконтактной решеткой, шаг 1,27 мм, 26 × 26 контактов, 35 × 35 мм, органическая подложка, крепление матрицы C4 (флип-чип)

- 16-битный интерфейс HyperTransport 3.0 до 1800 МГц, 3600 МТ/с, 7,2 ГБ/с в каждом направлении

- 2 × 64-битный интерфейс DDR2 SDRAM до 400 МГц, PC2-6400 (DDR2-800) , 12,8 ГБ/с

- До 2 небуферизованных модулей SO-DIMM, без поддержки ECC

- JEDEC SSTL_1.

8

8

- Управление питанием

- AMD PowerNow! технология

- До 8 P-состояний; ACPI C1, C1E, C2, C3, S1, S3, S5

- Самолеты с тройной силовой установкой

- Управление питанием канала HT

- Терморегуляторы

- Тепловая защита

- Аппаратный терморегулятор

- Тепловая защита DRAM

- Термодиод

Чипсеты[править]

- AMD M780G, M780V

- Драм 880М

- AMD SB700, SB710, SB820 южный мост

Процессоры, использующие Socket S1g20020

Схема упаковки[править]

Данные отсутствуют. Размеры должны быть такими же, как у корпуса OPGA-638, показанного на странице Socket S1g1.

Socket Outline #31839. Изображена технология Foxconn Interconnect Technology, часть № PZ6382A-284S-01F. Все размеры в миллиметрах.

Карта контактов[править]

Отличия от других версий Socket S1 см. в Socket S1g4.

Описание контакта[править]

| Сигнал | Описание |

|---|---|

| ALERT_L | Программируемый вывод, который может указывать на различные события, включая прерывание SB-TSI |

| CLKIN_H/L | Дифференциальная опорная частота ФАПЧ 200 МГц |

| DBREQ_L, DBRDY | Запрос отладки/готовность |

| HT_REF0, HT_REF1 | Компенсационный резистор HyperTransport для VSS, VLDT |

| КЛЮЧ1, КЛЮЧ2 | |

| L0_CADIN/OUT_H/L[15:0] | HT Link 0 Дифференциальная команда/адрес/ввод/вывод данных |

| L0_CLKIN/OUT_H/L[1:0] | HT Link 0 Дифференциальный тактовый вход/выход |

| L0_CTLIN_H/L[1:0] | HT Link 0 Дифференциальный вход/выход управления |

| LDTREQ_L | Канал HT активен или запрошен входом/выходом устройства |

| LDTSTOP_L | HT Вход управления остановкой для управления питанием и изменения ширины канала и частоты |

| MA0/MA1/MB0_CS_L[1:0], MB1_CS_L[0] | Выбор чипа DRAM |

| MA0/MA1/MB0_ODT[1:0], MB1_ODT[0] | Штырь включения DRAM для терминации на кристалле |

| MA/MB_ADD[15:0] | Адрес столбца/строки DRAM |

| МА/МБ_БАНК[2:0] | Адрес банка DRAM |

| МА/МБ_КАС_Л | Строб адреса столбца DRAM |

| MA/MB_CKE[1:0] | Включение часов DRAM |

| MA/MB_CLK_H/L[7/5/4/1] | Дифференциальный тактовый сигнал DRAM |

| MA/MB_DATA[63:0] | Шина данных DRAM |

| MA/MB_DM[7:0] | Маска данных DRAM |

| MA/MB_DQS_H/L[7:0] | Строб дифференциальных данных DRAM |

| МА/МБ_РАС_Л | Строб адреса строки DRAM |

| МА/МБ_WE_L | Разрешение записи DRAM |

| MEMHOT_L | Вход тепловой защиты DRAM |

| М_ВРЕФ | Опорное напряжение интерфейса DRAM |

| М_ЗП, М_ЗН | Компенсационный резистор для VSS, VDDIO |

| PROCHOT_L | Процессор в HTC-активном состоянии ввода/вывода |

| PWROK | Напряжения и CLKIN достигли заданной работы |

| СБРОС_L | Сброс процессора |

| РСВД | Зарезервировано |

| SIC, SID | Интерфейс датчика температуры боковой полосы (SB-TSI), часы, данные |

| СВК, СВД | Идентификатор последовательного напряжения, часы интерфейса, данные |

| ТСК, ТДИ, ТДО, ТМС, ТРСТ_Л | JTAG-интерфейс |

| ТЕСТ* | Тестовый сигнал |

| ТЕРМДА, ТЕРМДК | Термодиод Анод, Катод |

| ТЕРМТРИП_Л | Выход отключения термодатчика |

| VDD0 | Блок питания ядра 0 |

| VDD0_FB_H/L | Дифференциальная обратная связь к регулятору VDD0 |

| VDD1 | Блок питания ядра 1 |

| VDD1_FB_H/L | Дифференциальная обратная связь к регулятору VDD1 |

| ВДДА | Фильтрованное напряжение питания PLL |

| VDDIO | Блок питания кольца ввода/вывода DRAM |

| VDDIO_FB_H/L | Дифференциальная обратная связь к регулятору VDDIO |

| ВДНБ | Блок питания северного моста |

| ВДДНБ_ФБ_Х/Л | Дифференциальная обратная связь к регулятору VDDNB |

| VLDT_A/B | Блок питания кольца ввода/вывода HyperTransport |

| ВСС | Земля |

| ВТТ | Напряжение окончания DRAM |

| VTT_SENSE | Штифт монитора VTT |

Ссылки № 31839, версия 3.

01, 10 апреля 2007 г.

01, 10 апреля 2007 г.

См. также

Facts about «Socket S1g2 — AMD»

RDF feed

| designer | AMD + |

| first launched | June 4, 2008 + |

| instance of | package + |

| Сегмент рынка | Мобил + |

| Имя | Socket S1G2 + |

| TDP | |

| TDP | |

0139

0139